Суперскаларност

Суперскаларност обухвата облик паралелизма под називом паралелизм на нивоу наредбе унутар једног процесора. И зато омогућава бржи рад процесора него што би то било могуће са одређеном брзином процесорског клока. Суперскаларни процесор извршава више од једне наредбе по такту истовремено шаљући вишеструке наредбе редундантним функционалним јединицама процесора. Свака функционална јединица није посебно процесорско језгро већ извршни ресурс унутар једног процесора као што је аритметичко-логичка јединица, делом шифтер, или множач.

У Флиновој подели, суперскаларни процесори са једним језгром су класификовани као SISD процесори, док је вишејезгарни суперскаларни процесор класификован као MIMD процесор.

Док суперскаларни procesor такође има проточну обраду, проточна обрада и суперскаларна архитектура се разликују у побољшању учинка.

Суперскаларност се везује за више препознатљивих карактеристика (унутар датог језгра):

- Наредбе се издају са секвенцијалног протока наредби

- Процесорски хардвер динамички проверава зависност података између наредби у времену извршавања

- Процесор обрађује вишеструке наредбе по циклусу

Историја

уредиCDC 6600 Симора Креја из 1965. се често помиње као први суперскаларни дизајн. Intel i960CA (1988) и AMD 29000 серија 29050 (1990) микропроцесора били су први комерцијални суперскаларни микропроцесори са једним чипом. RISC (рачунар са смањеним скупом инструкција) процесори као ови били су први микропроцесори који су користили концепт суперскаларности, зато што RISC дизајн завршава у једноставном језгру, допуштајући, на тај начин, укључивање више функционалних јединица (као што су аритметичко-логичке јединице) на једном процесору у ограничено исоланираним временским правилима (због тога су RISC планови били бржи него CISC планови крајем 80-их и почетком 90-их година).

Осим процесора коришћених за ниско-енергетске апликације, уграђене системе и уређаје на батерије, суштински сви процесори опште намене развијени од 1998 су суперкаларни.

P5 Pentium био је први суперскаларни х86 процесор; Nx586, P6 Pentium Pro и AMD K5 су први модели који асинхроно претварају х86-инструкције у динамички микрокод као micro-op секвенце пре извршења у суперскаларној микроархитектури. Ово доводи до динамичког распореда баферованих парцијалних инструкција и паралелизму даје већу могућност екстрактовања, за разлику од кутих метода P5 Pentium-а; такође поједностављује спекулативна извршења и дозвољава више часовне фреквенције у поређењу са напреднијим моделима као што је Cyrix 6x86.

Скалар у Суперскалар

уредиНајједноставнији процесори су скаларни процесори. Свака инструкција коју изврши скаларни процесор контролише једну или две ставке података у исто време, за разлику од векторског процесора, који при извршавању наредби истовремено обрађује више ставки података. Аналогија је у разлици између скаларне и векторске аритметике. Суперскаларни процесор је комбинација ова два. Свака инструкција обрађује по једну ставку података, међутим постоје више редундантне функционалне јединице унутар сваког процесора, чиме више инструкција може обрадити засебне ставке података у исто време.

Суперскаларни процесорски дизајн истиче напредовање, и дозвољава употребу више функционалних јединица у сваком тренутку. Ово је добило на важности с обзиром на пораст броја јединица. Док први супескаларни процесори садрже две аритметичко-логичке јединице и само један FPU, модерни модели као што је PowerPC 970 поседују четири аритметичко-логичке јединице, два FPU-а и две SIMD јединице. Уколико диспечер не успе да одржава инструкције у свим овим јединицама, учинак система ће се смањити.

Суперскаларни процесор обично одржава стопу извршења на једној инструкцији по машинском циклусу. Али само обрађивање више инструкција истовремено не значи нужно да се ради о суперскаларној архитектури, јер проточна обрада, мултипроцесор или вишејезгарна архитектура постижу исто, служећи се другим методама.

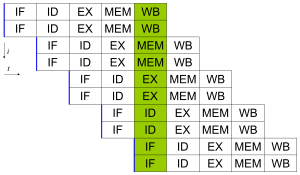

У суперскаларном процесору диспечер чита инструкције са меморије и одлучује које се могу покренути паралелно, шаљући их онда редудантним функционалним јединицама које су садржане унутар самог процесора. Из тог разлога, предвиђено је да суперскаларни процесор садржи вишеструке паралелне проточне обвраде, од којих свака симултано обрађује инструкције из једне нити инструкције.

Ограничења

уредиПобољшање учинка суперскаларним техникама ограничавају три кључне области:

- Степен унутрашњег паралелизма у инструкцији протока (инструкције које захтевају исте рачунарске ресурсе из процесора)

- Комплексност и временски трошкови слања и повезане зависности логичких провера

- Грана инструкција за обраду

Постојећи бинарни извршни програми имају различите степене унутрашњег паралелизма. У неким случајевима инструкције не зависе једне од других и могу се извршавати симултано. У другим случајевима оне су интер-зависне: на инструкцију утиче било ресурс или резултат друге инструкције. Инструкције: a = b + c; d = e + f могу се покренути паралелно зато што ни један од резултата не зависи од другог прорачуна. Међутим, инструкције: a = b + c; b = e + f не могу се покренути паралелно, у зависности од реда у којем се инструкције заврше крећући се кроз јединице.

Када се број издатих инструкција истовремено повећава, трошкови провере зависности расту изузетно брзо. Ово је погоршано потребом да се провере зависности у време извршавања и по такту централне процесорске јединице. Ова цена укључује додатна логичка кола, потребна за спровођење провера, а време успорава кроз та кола. Истраживање показује да цена кола у неким случајевима може бити , а цена кашњења , где је број инструкција у скупу инструкција процесора, а број истовремено послатих инструкција.

Иако ток инструкција не мора садржати зависности унутрашњих инструкција, суперскаларни процесор мора свакако проверити ту могућност, јер не постоји друга гаранција, а пропуст откривања зависност би произвео нетачне резултате.

Без обзира на то колико је напредан процес полупроводника или колика је брзина свичовања, ово представља ограничење на број истовремено преношених података. Док напредак процеса омогућава све већи број функционалних јединица , терет провере инструкција зависности расте тако брзо да је остварива суперскаларна граница слања јако мала, вероватмо по налогу пет до шест истовремено послатих инструкција.

Међутим, чак и ако нам је дата бесконачно брза логика за проверу зависности на иначе конвенционалном суперскаларном процесору, ако сам стирм инструкција има пуно завиности, то ће ограничити могуће убрзање. Тиме степен унутрашњег паралелизма у коду стрима формира друго ограничење.

Алтернативе

уредиКолективно, ова ограничења доводе истрагу до алтернативних архитектонских промена, као што су: Very Long Instruction Word (VLIW), Explicitly Parallel Instruction Computing (EPIC), истовремена вишенитна обрада (енгл. simultaneous multithreading, SMT), и вишејезгарни процесори.

Са VLIW-ом терет задатка провере зависности хардвер логике у времену извршавања је пребачен на компајлер. EPIC је као VLIW, са додатним инструкцијама за враћање података из кеша.

Истовремена вишенитна обрада (SMT) је техника за побољшање укупне ефикасности суперскаларних процесора. SMT дозвољава да више независних нити извршавања боље искористе ресурсе које омогућава модерна архитектура процесора.

Суперскаларни процесори се разликују од вишејезгарних процесора у томе што њима редудантне функционалне јединице нису у потпуности процесори. Један процесор се саставља од финијих функционалних јединица као што је аритметичко-логичка јединица, јединица за рад са целим бројевима, множач, јединица за рад са подацима са покретним зарезом, итд. Постоји више начина сваке функционалне јединице на које омогућавају паралелно извршавање. То није случај код вишејезгарних процесора који извршавају то преко нити и језгара (једна нит по језгру). Такође, то није случај ни код процесора са проточном обрадом где се вишеструке инструкције могу налазити у више фаза извршвања конкурентно.

Различите алтернативне технике се не искључују међусобно. Могу бити (и често јесу) комбиноване у једном процесору. Тиме језгара вишејезгарних процесора могу имати своје паралелне обраде при чему свака паралелна обрада може бити суперскалар. Неки процесори такође укључују способност векторског извршавања.

Види још

уредиЛитература

уреди- Mike Johnson (1991). Superscalar Microprocessor Design. Prentice-Hall. ISBN 978-0-13-875634-5.

- Sorin Cotofana, Stamatis Vassiliadis, "On the Design Complexity of the Issue Logic of Superscalar Machines", EUROMICRO 1998: 10277-10284

- Steven McGeady, "The i960CA SuperScalar Implementation of the 80960 Architecture", IEEE (1990). стр. 232–240

- Steven McGeady, et al., "Performance Enhancements in the Superscalar i960MM Embedded Microprocessor," ACM Proceedings of the 1991 Conference on Computer Architecture (Compcon), (1991). стр. 4–7

Спољашње везе

уреди- Eager Execution / Dual Path / Multiple Path, By Mark Smotherman